Audio and video surveillance is an important part of the security system. It is a comprehensive system with strong defense capabilities. Audio and video surveillance is widely used in many applications because of its intuitiveness, accuracy, timeliness and rich information content. In recent years, with the rapid development of computer, network and image processing and transmission technology, audio and video monitoring technology has also made great progress. Under the continuous development of audio and video technology, audio and video surveillance can be divided into two categories: digital audio and video surveillance systems and network surveillance (embedded audio and video surveillance systems).

Choose the right device for your application

Most audio and video capture devices support single channel and generate source synchronous digital signals in Y/Cr/Cb data format. Although DSPs have the ability to acquire digital audio and video signals, they can perform digital signal processing tasks, but usually only support a few channels. This design chose FPGA, which proved to be a good alternative for multi-channel input tasks and signal processing tasks.

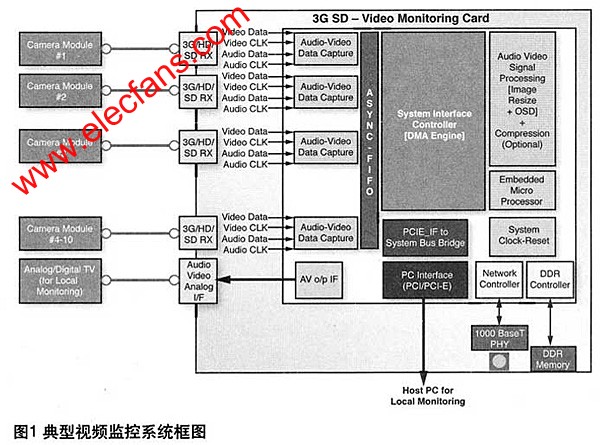

Figure 1 shows a typical secure video surveillance system with a 3G/SD/HD/SDI video interface. In this design, the camera transmits information in 3G-SDI format to the board, which in turn collects the data and converts it to 10-bit (Y/Cr/Cb format) source-synchronized video at the highest clock frequency of 145.5MHz. Data (10/20 bit interface). The board processes the source sync audio data at the highest clock frequency of 96 kHz.

Here, the memory capacity is 512Mb and the width is 32 bits, so the FPGA must support up to 2Gb of expansion capability.

For this design, the FPGA must support up to ten digital audio and video source sync input channels (20-bit source synchronous Y/Cr/Cb data format) and must be configurable in SD/HD data format. Other requirements include audio and video signal processing and optional compression algorithms, a central processing unit with an advanced DMA engine, and an audio and video output port for connecting a VGA display or a standard TV.

To meet these technical conditions, several factors must be considered when implementing the design. The main factors are clock requirement analysis, initial layout planning, core generation and IP integration, timing constraint definition, and timing analysis and timing correction after place and route. But first we have to decide on the choice of FPGA.

FPGA selection

FPGA (Field-Programmable Gate Array), which is a field-programmable gate array, is a product further developed on the basis of programmable devices such as PAL, GAL, and CPLD. It emerged as a semi-custom circuit in the field of application specific integrated circuits (ASIC), which not only solves the shortcomings of the custom circuit, but also overcomes the shortcomings of the limited number of original programmable device gates.

We choose based on several factors. The device needs to meet the expected I/O requirements and must have a corresponding number of logic cells, a suitable block RAM size, and a number of clock buffers and clock management devices such as phase-locked loop (PLL), digital clock management (DcM) Module and multiply accumulate modules. Based on these needs, we chose Virtex-5 XCVSX95T-FF1136.

Clock requirement analysis

After selecting the FPGA, we begin the design process, which analyzes the clock control requirements and then maps the signals to I/O banks or I/O pins.

For clock requirement analysis, it is important to consider the following factors: Does the FPGA have enough clock function I/O lines and global clock I/O lines? Is there enough PLL, DCM, and global clock buffer? Does the global clock I/O buffer support the highest frequency required?

The clock control requirements for this design include: a global system clock running at 150MHz-200MHz with several PLLs for all internal logic to process; a global clock running at 250MHz with a PCI Express link for PLL/DCM; A global clock buffer (with PLL and DCM) running at 250MHz is used for Ethernet MAC; and a 200MHz clock (generated by PLL/DCM) for bit-by-bit skewing in I/O modules.

We need a total of 4 to 6 global clock buffers and 16 local clock buffers. The FPGA XCVSX95T-FF1136 provides 20 global clock input pins and 4 clock function I/Os per group. The clock function pins of the I/O group can also be directly connected to the area buffer or I/O buffer and will It is used for a specific area or an adjacent area. In addition, each GTP/MGT has a reference clock input pin.

Initial layout planning

Virtex-5 FPGAs have a total of 18 I/O banks that map various input/output pairs to these I/O banks. There are several I/O groups that support 20 pairs of inputs/outputs or 10 global clocks. Most I/O groups support 40 pairs of inputs/outputs, and each input/output has 4 input clock function pins and 8 output clock function pins.

At the same time, the top and bottom FPGAs include three clock control modules (CMTs), one PLL and two DCMs. For all global clock signals that require PLLs in the upper and lower devices, we must ensure that they are properly mapped so that The design has a direct connection from the global clock input buffer to the PLL. Then we use the remaining 14 I/O groups that support 40 I/O lines in single-ended/differential mode. Each group consists of four single-ended clock function pins and eight differential clock function pins. The clock function pins can then be mapped or connected to the regional clock buffer or I/O clock buffer.

In general, these clock function pins and region buffers can be used to map the source synchronous clock input. The area buffer has a low degree of skew and can access three areas (the area where the area buffer is located, and one area above and below it). But for group selection of source synchronous data, we tend to use only one I/O group. If other IIOs are needed, it is best to use I/O groups for data signals that have been mapped to neighboring groups in advance.

The initial layout of the design is planned in a few steps. First place the system clock in the upper half and then place the auto-acquisition (optional) clock in the lower half. We have locked the CMT for each half to meet the 3/4 requirements of the I/O group. This mapping ensures that two PLL/DCM (CMT) are available for each half of the PCI (SGMII) function for PCI Express and Gigabit Ethernet.

The sync data is then mapped to the group containing the regional clock, so the 10 audio and video channel inputs are mapped to the remaining I/O banks. Each video channel consists of 20 data lines, 3 control signals, and 3 video clock inputs. At the same time, each audio channel is composed of 4 data signals, 3 control signals and 1 audio clock signal. This satisfies the requirement that at least two clock function pins be used for 32 signals.

For this design, 10 audio and video channels use 10 I/O groups. We mapped the video clock and audio clock to the clock function pins to ensure efficient use of the regional clock buffer and I/O clock buffer. According to the requirements of the PCB, we selected the 5th, 6th, 13th, 17th, 18th, 19th, 20th, 22nd and 25th groups for the audio and video channels.

For DDR memory, the design supports one 32-bit data bus, 14 address lines, and several control lines. We need 85~90 signals to map the DDR memory interface. Depending on the layout of the PCB, we used I/O banks 11, 23 and 15 to map all I/O signals of the DDR. Since the DDR memory operates according to the system clock, we have chosen to map the read data DQS signal generated by the DDR to the I/O line with clock function.

Nuclear generation and IP integration

Virtex-5 supports a variety of configurations of clock control modules that can be generated with the CORE Generator tool. These include several filter clock jitter PLLs, a PLL-DCM pair with filter clock jitter, a PLL-DCM pair with output double data rate (ODDR) or DCM, a standard phase-shift clock DCM and several dynamics Clock switching PLL.

To generate a PLL, you first need to know if the input is single-ended or differential. Then, you must determine if the clock jitter is appropriate and if a global buffer is used to buffer all the outputs.

To drive the clock in the source sync output using an ODDR flip-flop, we implemented a DCM that is used to drive the ODDR flip-flop to implement the associated clock control. This DCM runs in parallel with the DCM we use for internal clock control.

When generating a PCI Express core, we must ensure that the reference clock has the same performance (ie, 100MHz) as the PCI Express slot output on the PC motherboard. In addition, we also need to determine how many base register (BAR) the core needs, and whether the BAR is a memory map or an I/O map. We use a BAR monitor for address decoding, which can help generate BAR hit points.

When designing the bridge between PCI Express and the system local bus, we used BAR to access the memory map or I/O mapped registers or BlockRAM to ensure that the core and bus can access all registers or BlockRAM correctly.

If any of the above points are missed, the host PC will not get any response when attempting to pass and execute a read transaction. The host PC will enter an unknown state or generate an unrecoverable error.

IP is the abbreviation of English Internet Protocol (the protocol for interconnection between networks). Chinese is abbreviated as "network association", which is a protocol designed for communication between computer networks. In the Internet, it is a set of rules that enable all computer networks connected to the network to communicate with one another, defining the rules that computers should follow when communicating over the Internet. Any computer system produced by any manufacturer can be interconnected with the Internet as long as it complies with the IP protocol. IP addresses are unique and can be classified into five categories depending on the nature of the user. In addition, IP also has the meaning of entering protection, intellectual property, pointer registers and so on.

For IP integration, a separate clock reset module must be used for each FPGA. The asynchronous reset must be synchronized to each clock, either global or regional. Internally, the reset signal is asserted asynchronously and synchronously with respect to a particular clock, and its output is applied to the particular module to which each clock belongs. You need to ensure that all global input clocks have been connected to the PLL/DCM core generated with CoreGen.

Connect the area clock to BUFR/BUFIO. In addition, in order to avoid the layout and routing tools using unnecessary routing resources, only the necessary reset signals can be generated. It is necessary to ensure that the PLL/DCM latch condition is transferred to an external pin or configuration register. In the example, we only connected the PLL latch of the 200MHz system clock to the I/O pin.

Because we are designing with high-speed source synchronous inputs and outputs, the Virtex-5's bit-wise deskew function helps us meet setup and hold requirements at the input and output levels, and the bit-by-bit skew function is built into all I/O modules ( 10DELAY primitive). For source-synchronous inputs, the source-synchronous clock uses BUFIO or BUFR, thus introducing additional delay. To compensate for this delay, we drive the data and clock inputs through an IODELAY instance, which is configured in an input delay mode with a known delay count. We help to meet the timing requirements of the input stage by modifying the delay count value.

The situation at the output stage is similar. Because the synchronous clock signal is transmitted with the data, we need to ensure that the data and clock signals are transmitted in such a way as to meet the setup and hold requirements of the FPGA or ASIC at the other end. For both clock and data output, we have used an IODELAY instance configured in an output delay mode with a known delay count value.

Timing considerations and constraint definitions

After generating and implementing the IP, the next step is to perform the timing. We constrain the cycle, jitter, and input offset delays of all input clocks and set all output delays and input-to-output delays relative to the source clock. Timing and layout constraints are then established in the User Constraint File (UCF).

We constrain all input clocks to specific frequencies and define the jitter input with the following UCF code:

NET "i_clk_200_s"TNM_NET="IN_200_CLKGRP";TIMESPEC"IN_200_CLKGRP"=PERIOD5nsHIGH50%INPUT_JITTER0.1ns

For source synchronous data, in the case of SDR, we can set the input clock to a 0 degree phase shift or a 180 degree phase shift, and in the case of DDR it can be set to a 90 degree phase shift. Figure 2 shows the source synchronous DDR data input timing for the clock at 90 degree phase shift.

Figure 2 shows the source synchronous DDR data input timing for the clock at 90 degree phase shift.

For timing constraints on PCI Express cores and Gigabit Ethernet MAC cores, we used all timing and layout constraints for Block RAM and PLL/DCM as defined in the CORE Generator example.

Because many Virtex-5 designs use multiple asynchronous clocks, we must define dummy paths in our design so that these clocks are not affected.

Timing analysis and timing correction after place and route

After laying out the design, we ran static timing analysis (STA) and timing simulation to see if there were other timing errors. For STAs, we ensure that the timing report covers all paths with and without constraints. By using the STA report, we can identify input/output timing and internal system timing.

Virtex-5-based FPGAs have proven to be very suitable for our video surveillance systems. The regional clock buffer and I/O clock buffer enable us to support multi-channel source synchronous audio and video inputs. Moreover, the device's PCI Express and Gigabit Ethernet MAc hard macros provide us with the global connectivity needed for remote monitoring. In future design work, we will rely on pre-planning to ensure that the available resources of a particular FPGA are effectively used to design products with added value.

:

Industrial Rubber Hose,Industrial Rubber Hose Pipe,Industrial Rubber Hose Manufacturers,Industrial Rubber Hose Suppliers

Rubber Tube, Pipe & Hose Co., Lt d , http://www.nbhoses.com